Difference between revisions of "I/O modules"

(Created page with "{{Gotoparent|Hardware}} <div style="background-color: #f9f9f9; border: 1px solid #ccc; padding: 10px; margin-right: 10px; float: left;"> <div style="text-align: center; font-...") |

|||

| Line 12: | Line 12: | ||

<div class="clear"></div> | <div class="clear"></div> | ||

</div> | </div> | ||

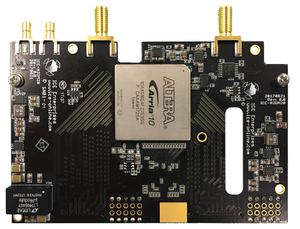

| − | [[File: | + | [[File:Ice-a2d-m20-top.png|thumb|ICE-A2D-M20]] |

The digital I/O module sites can be configured for four types of electrical interfaces: | The digital I/O module sites can be configured for four types of electrical interfaces: | ||

<ul style="list-style: none;"> | <ul style="list-style: none;"> | ||

Revision as of 14:56, 13 April 2020

The digital I/O module sites can be configured for four types of electrical interfaces:

- (S) 16-bit single-ended LVTTL

- (D) 16-bit LVDS

- (H) bidirectional 8-bit LVDS

- (R) 4-lane, bidirectional RocketIO

The connector accepts a ribbon cable connector or one of the 2×2.6in form factor modules listed below. The module sites use FPGAs to perform optional clock and MSB inversion, muxing/demuxing of data bits, packet parsing, and time code processing. The standard FPGA program supports 1-, 4-, 8-, or 16-bit data words, real or complex. If an ICE-A2D or ICE-D2E is connected, the FPGA can also be used to generate a sampling clock if not supplied externally. Dual-module sites are clocked independently to allow for short- or long-term clock skew or different sampling rates. They may also be locked to either one of the sources.

If you need to remove an I/O module on a ICE-PIC card, please click here for instructions. For specific measurements for PIC5+ I/O modules, please refer to the I/O Module Specifications page.

Note: SFP Transceivers are available from ICE for applicable I/O modules.