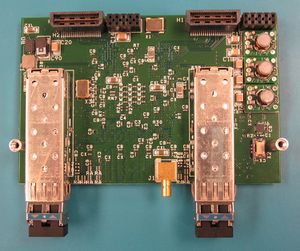

ICE-UDP-10G-r2

Jump to navigation

Jump to search

10Gbit UDP Module

Notice: End-of-Life has been announced for this product. It has been superseded by the ICE-UDP-10G-R3. Please see End-of-Life for details.

Contents

Features

- Hooks directly to 10GbE fiber optic network, for data acquisition/playback from/to a network at full 10GbE line rates

- Supports bidirectional network communications in one module

- Supports ARP/RARP protocols for remote IP address receipt or user-definable IP addresses

- Encapsulates UDP & IP protocols in hardware

- Ability to turn on or off VLAN tags

- Software: X-Midas/NeXtMidas and C user interfaces

Note: For use with the ICE-PIC6 card

Data Acquisition (Input) Modes

- IGMP support for dynamic multicast join/leaves/membership reports

- Currently supports up to 4 or 8 (depending on acquire mode), IGMP groups may be joined during a single acquisition

- "Raw" bit acquire mode: acquires ALL bits on the 10GbE fiber

- Raw packet acquire mode: acquires ALL packets regardless of type, removes inter-packet gap

- SDDS packet only mode (ethernet header, IP header, UDP header, SDDS header, and SDDS Data) acquire mode

- SDDS data & SDDS header acquire mode: all other packet headers discarded

- SDDS data acquire mode with all other packet headers discarded

- Hardware endian swapping options for incoming acquisitions

- Hardware support to check for dropped packets during a acquisition (missing sequence counters)

- Hardware support for "auto-fill" for missed packets so that sample timing may be maintained

- Support samples sizes: packed 4-bit data (2 4-bit samples per 8-bit slot), 6-bit data (zero-padded to 8), 8-bit, & 10-, 12-, 14-, 16-bit (zero-padded to 16)

- Ability to pull out time stamps from headers and provide offset/pointer to sample that is tied to that value

- Ability to filter SDDS parity packets and non-standard SDDS packets

- Onboard 512 MByte memory buffer for EACH channel to support "bursting" network routers (FPGA firmware under development: available 10/12)

- Support for input "ping-pong" mode from 2 fiber sources and reassembly into one data stream (FPGA firmware under development: available 10/12)

Data Playback (Output) Modes

- Raw data Tx mode: user supplies SDDS data only, TGSDDSxD module will insert network/SDDS headers for transmit on 10GbE fiber

- Raw data Tx Mode: automatic insertion of packet-count sequence in SDDS header

- Raw SDDS data Tx mode: user supplies SDDS data & SDDS header Only, TGSDDSxD module will insert network headers for transmit on 10GbE fiber

- User-selectable/programmable Tx packet sample rates available up to full 10GbE rates (SDDS data rate of 1100 MB/Sec) via onboard 10MHz reference or user-supplied 10Mhz reference

- Raw data or daw SDDS "ping-pong" output mode: allows for Tx operations of a single stream to both transceivers at up to 1400MB/Sec (data rate split across two fibers at 700MB/Sec)

- Use of external 10MHz reference allows user to lock to a dedicated site reference for coherent playback of multiple modules; if no site reference is available, then onboard reference can be used to generate Tx sample clock

Documentation

![]() Documentation for Flags and Examples of the Modules: [[1]]

Documentation for Flags and Examples of the Modules: [[1]]

Status and Configurations

EOL has been declared for this model: see End-of-Life for details. Please call for pricing and availability.

The standard configuration employs the 1310nm Fiber Interface.

If desired, 850nm fiber interface is available through special order. (Call for pricing).